# **PROCEEDINGS OF SPIE**

# Emerging Lithographic Technologies XI

Michael J. Lercel Editor

27 February–1 March 2007 San Jose, California, USA

Sponsored and Published by SPIE—The International Society for Optical Engineering

Cooperating Organization SEMATECH

Volume 6517

The International Society for Optical Engineering

Proceedings of SPIE—The International Society for Optical Engineering, 9780819466365, v. 6517

SPIE is an international technical society dedicated to advancing engineering and scientific applications of optical, photonic, imaging, electronic, and optoelectronic technologies.

The papers included in this volume were part of the technical conference cited on the cover and title page. Papers were selected and subject to review by the editors and conference program committee. Some conference presentations may not be available for publication. The papers published in these proceedings reflect the work and thoughts of the authors and are published herein as submitted. The publisher is not responsible for the validity of the information or for any outcomes resulting from reliance thereon.

Please use the following format to cite material from this book:

Author(s), "Title of Paper," in Emerging Lithographic Technologies XI, edited by Michael J. Lercel, Proceedings of SPIE Vol. 6517 (SPIE, Bellingham, WA, 2007) Article CID Number.

ISSN 0277-786X ISBN 9780819466365

Published by **SPIE—The International Society for Optical Engineering** P.O. Box 10, Bellingham, Washington 98227-0010 USA Telephone 1 360/676-3290 (Pacific Time) · Fax 1 360/647-1445 http://www.spie.org

Copyright © 2007, The Society of Photo-Optical Instrumentation Engineers

Copying of material in this book for internal or personal use, or for the internal or personal use of specific clients, beyond the fair use provisions granted by the U.S. Copyright Law is authorized by SPIE subject to payment of copying fees. The Transactional Reporting Service base fee for this volume is \$18.00 per article (or portion thereof), which should be paid directly to the Copyright Clearance Center (CCC), 222 Rosewood Drive, Danvers, MA 01923. Payment may also be made electronically through CCC Online at http://www.copyright.com. Other copying for republication, resale, advertising or promotion, or any form of systematic or multiple reproduction of any material in this book is prohibited except with permission in writing from the publisher. The CCC fee code is 0277-786X/07/\$18.00.

Printed in the United States of America.

# Contents

#### Part One

- xvii Symposium Committee

- xix Conference Committee

- xxi Plenary Paper: Lithography beyond 32nm: a role for imprint? M. Melliar-Smith, Molecular Imprints (USA)

#### **EUV SYSTEMS**

- 651705 SEMATECH's EUV program: a key enabler for EUVL introduction [6517-04] S. Wurm, C.-U. Jeon, M. Lercel, SEMATECH (USA)

- 651706 EUV lithography with the Alpha Demo Tools: status and challenges [6517-05]

N. Harned, ASML Wilton (USA); M. Goethals, IMEC (Belgium); R. Groeneveld, ASML Netherlands B.V. (Netherlands); P. Kuerz, M. Lowisch, Carl Zeiss Semiconductor Manufacturing Technologies AG (Germany); H. Meijer, H. Meiling, ASML Netherlands B.V. (Netherlands); K. Ronse, IMEC (Belgium); J. Ryan, M. Tittnich, CNSE/The Univ. at Albany (USA); H.-J. Voorma, ASML Netherlands B.V. (Netherlands); J. Zimmerman, ASML Wilton (USA); U. Mickan, S. Lok, ASML Netherlands B.V. (Netherlands)

- 651707 Nikon EUVL development progress update [6517-06]

T. Miura, K. Murakami, K. Suzuki, Y. Kohama, K. Morita, K. Hada, Y. Ohkubo, Nikon Corp. (Japan)

- 651708 Path to the HVM in EUVL through the development and evaluation of the SFET [6517-07] S. Uzawa, H. Kubo, Y. Miwa, T. Tsuji, H. Morishima, Canon Inc. (Japan)

# 651709 EUV lithography program at IMEC [6517-08] A. M. Goethals, R. Jonckheere, G. F. Lorusso, J. Hermans, F. Van Roey, IMEC (Belgium); A. Myers, M. Chandhok, Intel Corp. (USA); I. Kim, Samsung Electronics (South Korea); A. Niroomand, Micron Technology (USA); F. Iwamoto, Matsushita Electric Industrial Co., Ltd. (Japan); N. Stepanenko, Qimonda (USA); R. Gronheid, B. Baudemprez, K. Ronse, IMEC (Belgium)

**Pagination:** Proceedings of SPIE follow an e-First publication model, with papers published first online and then in print and on CD-ROM. Papers are published as they are submitted and meet publication criteria. A unique, consistent, permanent citation identifier (CID) number is assigned to each article at the time of the first publication. Utilization of CIDs allows articles to be fully citable as soon they are published online, and connects the same identifier to all online, print, and electronic versions of the publication.

SPIE uses a six-digit CID article numbering system in which:

• The first four digits correspond to the SPIE volume number.

• The last two digits indicate publication order within the volume using a Base 36 numbering system employing both numerals and letters. These two-number sets start with 00, 01, 02, 03, 04, 05, 06, 07, 08, 09, 0A, 0B ... 0Z, followed by 10-1Z, 20-2Z, etc.

The CID number appears on each page of the manuscript. The complete citation is used on the first page, and an abbreviated version on subsequent pages.

#### ADVANCED MASK I

- 65170A **Fast simulation of buried EUV mask defect interaction with absorber features** [6517-09] C. H. Clifford, A. R. Neureuther, Univ. of California, Berkeley (USA)

- 65170B **EUV MET printing and actinic imaging analysis on the effects of phase defects on wafer CDs** [6517-10] H. Han, SEMATECH (USA) and Samsung Electronics Co., Ltd. (South Korea); K. A. Goldberg,

H. Han, SEMATECH (USA) and Samsung Electronics Co., Ltd. (South Korea); K. A. Goldberg, A. Barty, E. M. Gullikson, Lawrence Berkeley National Lab. (USA); Y. Ikuta, T. Uno, SEMATECH (USA); O. R. Wood II, Advanced Micro Devices (USA); S. Wurm, SEMATECH (USA)

- 65170C **EUV and non-EUV inspection of reticle defect repair sites** [6517-11] K. A. Goldberg, Lawrence Berkeley National Lab. (USA); A. Barty, Lawrence Livermore National Lab. (USA); P. Seidel, SEMATECH (USA); K. Edinger, R. Fettig, Carl Zeiss SMS (Germany); P. Kearney, H. Han, SEMATECH (USA); O. R. Wood II, Advanced Micro Devices (USA)

- 65170D Inspection with the Lasertec M7360 at the SEMATECH Mask Blank Development Center [6517-12]

W. Cho, P. A. Kearney, SEMATECH MBDC (USA); E. M. Gullikson, Lawrence Berkeley National Lab. (USA); A. Jia, T. Tamura, A. Tajima, H. Kusunose, Lasertec Corp. (Japan); C.-U. Jeon, SEMATECH MBDC (USA)

65170E **EUVL mask substrate defect print study** [6517-13] J. Cullins, Y. Tezuka, I. Nishiyama, T. Hashimoto, Association of Super Advanced Electronics Technologies (Japan); T. Shoki, HOYA Corp. (Japan)

#### EUV OPTICS

- 65170F Atomic hydrogen cleaning of Ru-capped EUV multilayer mirror [6517-14] K. Motai, EUV Process Technology Research Laboratory, ASET (Japan); H. Oizumi, EUV Process Technology Research Laboratory, ASET (Japan) and Kyushu Institute of Technology (Japan); S. Miyagaki, I. Nishiyama, EUV Process Technology Research Laboratory, ASET (Japan); A. Izumi, T. Ueno, Y. Miyazaki, A. Namiki, Kyushu Institute of Technology (Japan)

- 65170G Critical parameters influencing the EUV-induced damage of Ru-capped multilayer mirrors [6517-15]

S. B. Hill, I. Ermanoski, C. Tarrio, T. B. Lucatorto, National Institute of Standards and Technology (USA); T. E. Madey, Rutgers Univ. (USA); S. Bajt, Lawrence Livermore National Lab. (USA); M. Fang, M. Chandhok, Intel Corp. (USA)

- 651701 Enhanced reflectance of interface engineered Mo/Si multilayers produced by thermal particle deposition [6517-17]

A. E. Yakshin, R. W. E. van de Kruijs, I. Nedelcu, E. Zoethout, E. Louis, F. Bijkerk, FOM Institute for Plasma Physics Rijnhuizen (Netherlands); H. Enkish, S. Müllender, Carl Zeiss SMT AG (Germany)

- 65170J Development of optics for EUV lithography tools [6517-18]

K. Murakami, T. Oshino, H. Kondo, H. Chiba, H. Komatsuda, K. Nomura, H. Iwata, Nikon Corp. (Japan)

| N | 11 |  |

|---|----|--|

| N |    |  |

- 65170K **Multilevel step and flash imprint lithography for direct patterning of dielectrics** [6517-19] W.-L. Jen, F. Palmieri, B. Chao, M. Lin, J. Hao, The Univ. of Texas/Austin (USA); J. Owens, K. Sotoodeh, ATDF, Inc. (USA); R. Cheung, Applied Materials (USA); C. G. Willson, The Univ. of Texas/Austin (USA)

- 65170L A study of imprint-specific defects in the step and flash imprint lithography process

[6517-20]

J. Perez, K. Selinidis, S. Johnson, B. Fletcher, F. Xu, J. Maltabes, I. McMackin, D. Resnick,

S. V. Sreenivasan, Molecular Imprints, Inc. (USA)

- 65170M Critical issues study of nano-imprint tool for semiconductor volume production [6517-21] H. Ina, K. Kasumi, E. Kawakami, K. Uda, Canon Inc. (Japan)

#### 65170N **Demolding strategy to improve the hot embossing throughput** [6517-22] T. Leveder, S. Landis, CEA - Leti Minatec (France); L. Davoust, LEGI/ENSHMG (France); S. Soulan, N. Chaix, CNRS-LTM (France)

#### EUV SOURCE I

- 651700 Laser-produced EUV light source development for HVM [6517-23]

A. Endo, H. Hoshino, T. Suganuma, M. Moriya, T. Ariga, Y. Ueno, M. Nakano, T. Asayama, T. Abe, H. Komori, G. Soumagne, H. Mizoguchi, A. Sumitani, K. Toyoda, Extreme Ultraviolet Lithography System Development Association (Japan)

- 65170P **EUV source development for high-volume chip manufacturing tools** [6517-24] U. Stamm, M. Yoshioka, J. Kleinschmidt, C. Ziener, G. Schriever, M. C. Schürmann, G. Hergenhan, XTREME technologies (Germany); V. M. Borisov, SRC RF TRINITI (Russia)

- 65170Q LPP EUV source development for HVM [6517-25]

D. C. Brandt, I. V. Fomenkov, A. I. Ershov, W. N. Partlo, D. W. Myers, N. R. Böwering,

A. N. Bykanov, G. O. Vaschenko, O. V. Khodykin, J. R. Hoffman, E. Vargas L., R. D. Simmons,

J. A. Chavez, C. P. Chrobak, Cymer, Inc. (USA)

# 65170S Tin inventory for HVM EUVL sources [6517-27] M. C. Richardson, K. Takenoshita, T. Schmid, College of Optics & Photonics/Univ. of Central Florida (USA)

65170T Microdischarge EUV source array and illuminator design for a prototype lithography tool [6517-28]

B. E. Jurczyk, R. A. Stubbers, D. A. Alman, Starfire Industries LLC (USA); R. Hudyma, M. Thomas, Hyperion Development LLC (USA)

#### EUV IMAGING I

| 65170U | Initial experience establishing an EUV baseline lithography process for manufacturability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | <ul> <li>assessment [6517-29]</li> <li>O. R. Wood II, Advanced Micro Devices (USA); D. Back, Qimonda North America (USA);</li> <li>R. Brainard, G. Denbeaux, Univ. at Albany (USA); D. Goldfarb, IBM T.J. Watson Research Ctr. (USA); F. Goodwin, Qimonda North America (USA); J. Hartley, Univ. at Albany (USA);</li> <li>K. Kimmel, C. Koay, IBM Corp. (USA); B. La Fontaine, Advanced Micro Devices (USA);</li> <li>J. Mackey, Micron Technology (USA); B. Martinick, Qimonda North America (USA);</li> <li>W. Montgomery, P. Naulleau, Univ. at Albany (USA); U. Okoroanyanwu, Advanced Micro Devices (USA);</li> <li>K. Petrillo, IBM Corp. (USA); B. Pierson, ASML (USA); M. Tittnich, Univ. at Albany (USA);</li> <li>S. Trogisch, Qimonda Dresden GmbH (Germany); T. Wallow, Advanced Micro Devices (USA); Y. Wei, Qimonda North America (USA)</li> </ul> |  |  |  |

| 65170V | Recent results from the Berkeley 0.3-NA EUV microfield exposure tool [6517-30]<br>P. P. Naulleau, Lawrence Berkeley National Lab. (USA); C. N. Anderson, Univ. of<br>California/Berkeley (USA); K. Dean, SEMATECH (USA); P. Denham, K. A. Goldberg, B. Hoef,<br>Lawrence Berkeley National Lab. (USA); B. La Fontaine, T. Wallow, Advanced Micro<br>Devices (USA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 65170W | EUVL mask dual pods to be used for mask shipping and handling in exposure tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|        | [6517-31]<br>Y. Gomei, Canon Inc. (Japan); K. Ota, Nikon Corp. (Japan); J. Lystad, D. Halbmair, Entegris,<br>Inc. (USA); L. He, SEMATECH North (USA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 65170X | Assessment of pattern position shift for defocusing in EUV lithography [6517-32]<br>M. Sugawara, Sony Electronics Inc. (USA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 65170Y | <b>Electrostatic chucking of EUVL reticles</b> [6517-33]<br>M. Nataraju, J. Sohn, A. R. Mikkelson, R. L. Engelstad, K. T. Turner, Univ. of Wisconsin/Madison<br>(USA); C. K. Van Peski, K. J. Orvek, SEMATECH Inc. (USA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|        | MASKLESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 65170Z | Technology mapping technique for enhancing throughput of multi-column-cell systems [6517-34]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|        | M. Sugihara, ISIT (Japan); Y. Matsunaga, K. Murakami, Kyushu Univ. (Japan)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 651710 | <b>Stage position measurement for e-beam lithography tool</b> [6517-35]<br>P. G. Harris, Vistec Lithography Ltd. (United Kingdom); W. Lee, Renishaw plc (United<br>Kingdom); A. W. McClelland, J. M. Tingay, Vistec Lithography Ltd. (United Kingdom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 651711 | Defect inspection of positive and negative sub-60nm resist pattern printed with variable<br>shaped e-beam direct write lithography [6517-36]<br>C. Arndt, C. Hohle, J. Kretz, T. Lutz, Qimonda Dresden GmbH (Germany); M. Richter,<br>Infineon Technologies Dresden GmbH (Germany); K. Keil, Fraunhofer CNT (Germany);<br>M. Lapidot, D. Zemach, M. Kindler, NEGEVTECH GmbH (Germany)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 651712 | <b>A study of voltage contrast image using Monte Carlo simulation</b> [6517-37]<br>T. Ota, T. Koshiba, T. Nakasugi, Toshiba Corp. (Japan)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

# 651713 Alignment method of low-energy electron-beam direct writing system EBIS using voltage contrast image [6517-38]

T. Koshiba, T. Ota, T. Nakasugi, Toshiba Corp. (Japan); F. Nakamura, K. Watanabe, K. Sugihara, e-BEAM Corp. (Japan)

#### NIL II

# 651714 An electrical defectivity characterization of wafers imprinted with step and flash imprint lithography [6517-39]

W. J. Dauksher, N. V. Le, K. A. Gehoski, E. S. Ainley, K. J. Nordquist, Motorola Labs. (USA); N. Joshi, Florida International Univ. (USA)

# 651715 Nanoimprint lithography for the direct patterning of nanoporous interlayer dielectric insulator materials [6517-40]

H. W. Ro, H.-J. Lee, E. K. Lin, A. Karim, NIST Polymers Division (USA); D. R. Hines, Univ. of Maryland, College Park (USA); D. Y. Yoon, Seoul National Univ. (South Korea); C. L. Soles, NIST Polymers Division (USA)

#### 651716 Ultra-violet nanoimprint lithography applicable to thin-film transistor liquid-crystal display [6517-41]

J. Jeong, K. Kim, D. Choi, J. Choi, E. Lee, Korea Institute of Machinery and Materials (South Korea)

### 651717 Toward 22 nm for unit process development using step and flash imprint lithography [6517-42] G. M. Schmid, E. Thompson, N. Stacey, D. J. Resnick, Molecular Imprints, Inc. (USA);

G. M. Schmid, E. Thompson, N. Stacey, D. J. Resnick, Molecular Imprints, Inc. (USA); D. L. Olynick, E. H. Anderson, Lawrence Berkeley National Lab. (USA)

#### 651718 Soft UV-based nanoimprint lithography for large-area imprinting applications [6517-43] T. Glinsner, EV Group (Austria); U. Plachetka, AMICA/AMO (Germany); T. Matthias, M. Wimplinger, EV Group Inc. (USA); P. Lindner, EV Group (Austria)

#### JOINT SESSION WITH CONFERENCE 6519: EUV RESIST

Solak, Paul Scherrer Institute (Switzerland)

651719 Chemically amplified resists resolving 25 nm 1:1 line: space features with EUV lithography [6517-44]

J. W. Thackeray, R. A. Nassar, Rohm and Haas Electronic Materials (USA); R. Brainard, Univ. at Albany (USA); D. Goldfarb, IBM Microelectronics Research (USA); T. Wallow, Advanced Micro Devices (USA); Y. Wei, Qimonda North America Corp. (USA); J. Mackey, Micron Technology Inc. (USA); P. Naulleau, Univ. at Albany (USA); B. Pierson, ASML (USA); H. H.

#### ADVANCED MASK II

65171D New requirements for the cleaning of EUV mask blanks [6517-48] A. Rastegar, S. Eichenlaub, V. Kapila, A. J. Kadaksham, SEMATECH (USA); P. Marmillion, IBM (USA)

#### 65171E Experimental and simulation investigations of acoustic cavitation in megasonic cleaning [6517-49]

K. Muralidharan, M. Keswani, H. Shende, P. Deymier, Univ. of Arizona (USA); S. Raghavan, Univ. of Arizona (USA) and Intel Corp. (USA); F. Eschbach, A. Sengupta, Intel Corp. (USA)

- 65171F Photonic band-gap masks to enhance resolution and depth of focus [6517-50] J. Nistler, K. Duckworth, Psida Lithography & Software LLC (USA); J. Chaloupka, Masaryk Univ. (Czech Republic); M. Brock, Psida Lithography & Software LLC (USA)

- 65171G Properties of EUVL masks as a function of capping layer and absorber stack structures

[6517-51]

H.-S. Seo, J. Park, S.-Y. Lee, J.-O. Park, H. Kim, S.-S. Kim, H.-K. Cho, Samsung Electronics Co.,

Ltd. (South Korea)

#### NOVEL LITHOGRAPHY

- 651711 **Molecular-ruler nanolithography** [6517-53] C. Srinivasan, J. N. Hohman, M. E. Anderson, P. Zhang, P. S. Weiss, M. W. Horn, The Pennsylvania State Univ. (USA)

- Scissionable bile acid nanostructures for lithography [6517-54]

R. P. Meagley, Lawrence Berkeley National Lab. (USA) and Intel Corp. (USA); G. Sharma, Intel Corp. (USA); A. Guptab, Lawrence Berkeley National Lab. (USA) and Intel Corp. (USA)

- 65171K Stretched polymer nanohairs by nanodrawing [6517-55] H. E. Jeong, S. H. Lee, P. Kim, K. Y. Suh, Seoul National Univ. (South Korea)

- birect three-dimensional nanoscale thermal lithography at high speeds using heated atomic force microscope cantilevers [6517-56]

Y. Hua, S. Saxena, J. C. Lee, W. P. King, C. L. Henderson, Georgia Institute of Technology (USA)

- Focused ion beam nano patterning for fabrications of III-nitride light emitting diodes

[6517-57]

M. Y. Kim, Y. C. Park, S. S. Hong, B. K. Kim, D. W. Kim, D. Y. Lee, Samsung Electro-Mechanics

(South Korea)

#### **EUV IMAGING II**

- 65171N **Rigorous model for registration error due to EUV reticle non-flatness and a proposed disposition and compensation technique** [6517-58] B. Lieberman, Intel Corp. (USA)

- 651710 Status and path to a final EUVL reticle-handling solution [6517-59]

L. He, K. Orvek, SEMATECH North (USA); P. Seidel, S. Wurm, SEMATECH (USA); J. Underwood,

E. Betancourt, SEMATECH North (USA)

- 65171P Performance estimation of EUV exposure optics for below 32-nm node in consideration of Mo/Si multilayer coating [6517-60]

T. Sasaki, K. Kajiyama, H. Morishima, T. Tsuji, M. Suzuki, M. Suzuki, H. Yokota, Canon Inc. (Japan)

#### Part Two

\_\_\_\_

|         | EUV SOURCE II                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 65171\$ | Thermal management design and verification of collector optics into high-power EUV<br>source systems [6517-63]<br>G. Bianucci, F. E. Zocchi, G. Pirovano, G. L. Cassol, F. Marioni, P. Binda, Media Lario<br>Technologies (Italy); L. Porreca, Eidgenössische Technische Hochschule (Switzerland);<br>I. Ahmad, D. Bolshukhin, M. C. Schürmann, XTREME technologies GmbH (Germany) |

| 65171T  | Low-cost EUV collector development: design, process, and fabrication [6517-64]<br>R. D. Venables, M. Goldstein, Intel Corp. (USA); D. Engelhaupt, Univ. of Alabama, Huntsville<br>(USA); S. H. Lee, E. M. Panning, Intel Corp. (USA)                                                                                                                                               |

| 65171V  | Energetic and thermal Sn interactions and their effect on EUVL source collector mirror<br>lifetime at high temperatures [6517-66]<br>J. P. Allain, M. Nieto, M. Hendricks, A. Hassanein, Argonne National Lab. (USA); C. Tarrio,<br>S. Grantham, National Institute of Standards and Technology (USA); V. Bakshi, SEMATECH<br>(USA)                                                |

| 65171W  | Application of the Energetiq EQ-10 electrodeless Z-Pinch EUV light source in outgassing<br>and exposure of EUV photoresist [6517-67]<br>P. A. Blackborow, D. S. Gustafson, D. K. Smith, M. M. Besen, S. F. Horne, R. J. D'Agostino,<br>Energetiq Technology, Inc. (USA); Y. Minami, Litho Tech Japan Co. (Japan); G. Denbeaux,<br>SUNY, Albany (USA)                               |

| 65171X  | <b>Optimization of EUV laser and discharge devices for high-volume manufacturing</b> [6517-68]<br>A. Hassanein, V. Sizyuk, T. Sizyuk, V. Morozov, Argonne National Lab. (USA)                                                                                                                                                                                                      |

|         | POSTER SESSION: ADVANCED MASK                                                                                                                                                                                                                                                                                                                                                      |

| 65171Y  | Detection signal analysis of actinic inspection of EUV mask blanks using dark-field imaging<br>[6517-69]<br>T. Tanaka, T. Terasawa, MIRAI-Selete (Japan); N. Iriki, Selete (Japan); H. Aoyama, MIRAI-<br>Selete (Japan); T. Tomie, AIST (Japan)                                                                                                                                    |

| 65171Z  | <b>Development of EUV mask handling technology at MIRAI-Selete</b> [6517-70]<br>K. Ota, M. Amemiya, T. Taguchi, T. Kamono, H. Kubo, T. Takikawa, Y. Usui, O. Suga,<br>Semiconductor Leading Edge Technologies, Inc. (Japan)                                                                                                                                                        |

| 651720  | Impact of interface treatment with assisted ion beam on Mo-Si multilayer formation for<br>EUVL mask blanks [6517-71]<br>K. Hiruma, Y. Tanaka, S. Miyagaki, J. Cullins, I. Nishiyama, Association of Super-Advanced<br>Electronics Technologies (Japan)                                                                                                                             |

| 651721  | Spectrally investigated optimization for high optical transmission of the C-shaped nano apertures [6517-72]<br>E. Lee, K. Kim, J. W. Hahn, Yonsei Univ. (South Korea)                                                                                                                                                                                                              |

| 651722  | Design of metal slits for higher harmonic fringe patterns generated with surface plasmon interference lithography [6517-73]<br>Y. Lee, S. Park, E. Lee, K. Kim, J. W. Hahn, Yonsei Univ. (South Korea)                                                                                                                                                                             |

- The effect of localized mask density variations on image quality in EUV lithography

[6517-74]

J. Park, H. Seo, S.-S. Kim, H. Cho, J.-T. Moon, Samsung Electronics Co., Ltd. (South Korea)

- 651724 **Corning ULE glass can meet P-37 specifications** [6517-75] W. Rosch, L. Beall, J. Maxon, R. Sabia, R. Sell, Corning Inc. (USA)

- 651725 **Evaluation and selection of EUVL-grade TiO<sub>2</sub>-SiO<sub>2</sub> ultra-low-expansion glasses using the line-focus-beam ultrasonic material characterization system** [6517-76] M. Arakawa, Y. Ohashi, J. Kushibiki, Tohoku Univ. (Japan)

- 651726 Defect mitigation and reduction in EUVL mask blanks [6517-77]

R. Randive, Veeco Instruments, Inc. (USA); A. Ma, SEMATECH (USA); I. Reiss, P. Mirkarimi,

E. Spiller, Veeco Instruments, Inc. (USA); B. Beier, T. Uno, P. Kearney, C.-U. Jeon, SEMATECH (USA)

#### POSTER SESSION: NANO-IMPRINT

- 651727 Low-viscosity and fast-curing polymer system for UV-based nanoimprint lithography and its processing [6517-78]

M. Vogler, micro resist technology GmbH (Germany); M. Bender, U. Plachetka, A. Fuchs, AMO GmbH (Germany); S. Wiedenberg, F. Reuther, G. Grützner, micro resist technology GmbH (Germany); H. Kurz, AMO GmbH (Germany)

- 651729 Photocurable silicon-based materials for imprinting lithography [6517-80]

J. Hao, M. W. Lin, F. Palmieri, Y. Nishimura, H.-L. Chao, M. D. Stewart, A. Collins, K. Jen,

C. G. Willson, The Univ. of Texas at Austin (USA)

- 65172A Nanoimprinting with SU-8 epoxy resists [6517-81]

D. W. Johnson, H. Miller, MicroChem Corp. (USA); M. Kubenz, F. Reuther, G. Gruetzner, micro resist technology GmbH (Germany)

- 65172B mr-NIL 6000: new epoxy-based curing resist for efficient processing in combined thermal and UV nanoimprint lithography [6517-82]

C. Schuster, M. Kubenz, F. Reuther, M. Fink, G. Gruetzner, micro resist technology GmbH (Germany)

- 65172C Structure and stability characterization of anti-adhesion self-assembled monolayers formed by vapor deposition for NIL use [6517-83]

S. Garidel, CEA LETI-MINATEC (France); M. Zelsmann, LTM-CNRS (France); P. Voisin, CEA LETI-MINATEC (France), LTM-CNRS (France), and ST Microelectronics (France); N. Rochat, P. Michallon, CEA LETI-MINATEC (France)

- 65172D Template flatness issue for UV curing nanoimprint lithography [6517-84]

P. Voisin, ST Microelectronics (France), CNRS/LTM, CEA Grenoble (France), and CEA/LETI (France); A. Jouve, M. Zelsmann, C. Gourgon, J. Boussey, CNRS/LTM, CEA Grenoble (France)

- 65172E Imprint solutions, costs, and returns of patterning LEDs [6517-86] M. P. C. Watts, Impattern Solutions (USA)

Whole wafer imprint patterning using step and flash imprint lithography: a manufacturing solution for sub-100-nm patterning [6517-87]

D. Lentz, G. Doyle, M. Miller, G. Schmidt, M. Ganapathisuramanian, X. Lu, D. Resnick, D. L. LaBrake, Molecular Imprints, Inc. (USA)

#### POSTER SESSION: ML AND E-BEAM LITHOGRAPHY

- Exposure characteristics of character projection-type low-energy electron-beam direct writing system [6517-88]

T. Satoh, R. Inanami, K. Kishimoto, K. Hirose, e-BEAM Corp. (Japan); T. Nakasugi, T. Koshiba, T. Ota, Toshiba Corp. (Japan)

- 65172H Data processing system in electron beam direct writing to obtain photolithography friendly resist patterns [6517-89]

H. Hoshino, Y. Machida, Fujitsu Ltd. (Japan)

- 651721 Recent progress of a character projection-type low-energy electron-beam direct writing system [6517-90]

K. Noguchi, K. Watanabe, H. Kinoshita, H. Shinozaki, Y. Kojima, S. Morita, F. Nakamura, N. Yamaguchi, K. Kushitani, e-BEAM Corp. (Japan); T. Nakasugi, T. Koshiba, T. Oota, Toshiba Corp. (Japan)

- 65172J Shot noise effect on LER and throughput in LEEPL system [6517-91] T. Utsumi, Nanolith LLC (Japan)

#### POSTER SESSION: EUV IMAGING

- 65172K **CD budget analysis on hole pattern in EUVL** [6517-92] N. Iriki, H. Aoyama, T. Tanaka, Semiconductor Leading Edge Technologies, Inc. (Japan)

- 65172L **Fidelity of rectangular patterns printed with 0.3-NA MET optics** [6517-93] Y. Tanaka, Y. Kikuchi, D. Goo, I. Nishiyama, Association of Super-Advanced Electronics Technologies (Japan)

- EUV exposure experiment using programmed multilayer defects for refining printability simulation [6517-94]

Y. Tezuka, J. Cullins, Y. Tanaka, T. Hashimoto, I. Nishiyama, Association of Super-Advanced Electronics Technologies (Japan); T. Shoki, HOYA Corp. (Japan)

- 65172N Lithographic metrics for the determination of intrinsic resolution limits in EUV resists [6517-95]

P. P. Naulleau, Lawrence Berkeley National Lab. (USA) and Univ. at Albany (USA);

C. N. Anderson, Univ. of California/Berkeley (USA); B. La Fontaine, R. Kim, T. Wallow, Advanced Micro Devices, Inc. (USA)

- 651720 Absorption of extreme ultraviolet radiation in photoresists [6517-96] R. Garg, A. Antohe, G. Denbeaux, SUNY/Albany (USA)

- 65172P Process window study with various illuminations for EUV lithography applications [6517-98] S. H. Lee, Z. Zhang, Intel Corp. (USA)

- 65172Q Characterization of low-order aberrations in the SEMATECH Albany MET tool [6517-99] P. Naulleau, Univ. at Albany (USA) and Lawrence Berkeley National Lab. (USA); J. Waterman, Univ. at Albany (USA); K. Dean, SEMATECH (USA)

- 65172S Characteristics and prevention of pattern collapse in EUV lithography [6517-101]

W. Chang, E.-J. Kim, Y.-M. Kang, S.-W. Park, Hanyang Univ. (South Korea); C.-M. Lim, Hynix Semiconductor Inc. (South Korea); K.-T. Won, J.-S. Kim, Seoul National Univ. (South Korea); H.-K. Oh, Hanyang Univ. (South Korea)

- 65172T **Extreme ultraviolet interference lithography with incoherent light** [6517-102] P. P. Naulleau, Lawrence Berkeley National Lab. (USA); C. N. Anderson, Univ. of California, Berkeley (USA); S. F. Horne, Energetiq Technology Inc. (USA)

- 651720 A short-pulsed laser cleaning system for EUVL tool [6517-103] M. Yonekawa, H. Namba, T. Hayashi, Y. Watanabe, Canon Inc. (Japan)

#### POSTER SESSION: EUV OPTICS

- 65172W **Polarization dependence of multilayer reflectance in the EUV spectral range** [6517-106] F. Scholze, C. Laubis, C. Buchholz, A. Fischer, A. Kampe, S. Plöger, F. Scholz, G. Ulm, Physikalisch-Technische Bundesanstalt (Germany)

- 65172X Carbon deposition on multi-layer mirrors by extreme ultra violet ray irradiation [6517-107]

S. Matsunari, T. Aoki, K. Murakami, Extreme Ultraviolet Lithography System Development Association (Japan); Y. Gomei, Canon Inc. (Japan); S. Terashima, H. Takase, M. Tanabe, Y. Watanabe, Extreme Ultraviolet Lithography System Development Association (Japan); Y. Kakutani, M. Niibe, Univ. of Hyogo (Japan); Y. Fukuda, Extreme Ultraviolet Lithography System Development Association (Japan)

- Effect of deposition, sputtering, and evaporation of lithium debris buildup on EUV optics [6517-108]

M. J. Neumann, M. Cruce, P. Brown, S. N. Srivasta, D. N. Ruzic, Univ. of Illinois at Urbana-Champaign (USA); O. Khodykin, Cymer (USA)

#### 65172Z Carbon accumulation and mitigation processes, and secondary electron yields of ruthenium surfaces [6517-109] B. V. Yakshinskiy, R. Wasielewski, E. Loginova, T. E. Madey, Rutgers, The State Univ. of New Jersey (USA)

- 651730 Substrate recovery layers for EUVL optics: effects on multilayer reflectivity and surface roughness [6517-110]

I. Nedelcu, R. W. E. van de Kruijs, A. E. Yakshin, E. Louis, F. Bijkerk, FOM-Institute for Plasma Physics Rijnhuizen (Netherlands); S. Mullender, Carl Zeiss SMT AG (Germany)

- 651731 Long-term durability of a Ru capping layer for EUVL projection optics by introducing ethanol [6517-111]

Y. Kakutani, M. Niibe, Univ. of Hyogo (Japan); Y. Gomei, Canon Inc. (Japan); H. Takase, S. Terashima, S. Matsunari, T. Aoki, Y. Fukuda, Extreme Ultraviolet Lithography System Development Association (Japan)

- 651732 **High-accuracy EUV reflectometer** [6517-112] U. Hinze, M. Fokoua, B. Chichkov, Laser Zentrum Hannover e.V. (Germany)

651733 Development of optical component for EUV phase-shift microscopes [6517-113]

Y. Mizuta, M. Osugi, J. Kishimoto, Univ. of Hyogo (Japan) and CREST-JST (Japan); N. Sakaya,

K. Hamamoto, HOYA Corp. (Japan) and CREST-JST (Japan); T. Watanabe, H. Kinoshita,

Univ. of Hyogo (Japan) and CREST-JST (Japan)

#### POSTER SESSION: NANOTECHNOLOGY

- 651734 Fabrication of fine pitch gratings by holography, electron-beam lithography, and nanoimprint lithography [6517-116]

D. Goodchild, A. Bogdanov, S. Wingar, B. Benyon, N. Kim, F. Shepherd, National Research Council of Canada (Canada)

- 651735 Three-dimensional x-ray lithography using a silicon mask with inclined absorbers

[6517-117]

H. Mekaru, T. Takano, K. Awazu, M. Takahashi, R. Maeda, National Institute of Advanced

Industrial Science and Technology (Japan)

- 651736 Photon sieve array x-ray maskless nanolithography [6517-118]

G. Cheng, Institute of Optics and Electronics (China) and Graduate School, Chinese Academy of Sciences (China); T. Xing, W. Lin, J. Zhou, C. Qiu, Institute of Optics and Electronics (China); Z. Liao, Y. Yang, Institute of Optics and Electronics (China) and Graduate School, Chinese Academy of Sciences (China); L. Hong, Univ. of Electronic Science and Technology of China (China); J. Ma, Taishan College (China)

- 651737 Magneto-polymer composite particles fabricated utilizing patterned perfluoropolyether elastomer molds [6517-119]

K. P. Herlihy, Univ. of North Carolina at Chapel Hill (USA); J. M. DeSimone, Univ. of North Carolina at Chapel Hill (USA) and North Carolina State Univ. (USA)

- 651738 Simulating droplet dynamics during evaporation-driven self-assembly [6517-120] J. J. Dyreby, K. T. Turner, G. F. Nellis, Univ. of Wisconsin-Madison (USA)

#### POSTER SESSION: EUV SOURCE

- 651739 Microfocus EUV tube for at-wavelength reflectometry [6517-121] A. Egbert, S. Becker, phoenix | euv Systems + Services GmbH (Germany)

- 65173B Characterization of various Sn targets with respect to debris and fast ion generation [6517-123]

Y. Ueno, H. Hoshino, T. Ariga, T. Miura, M. Nakano, H. Komori, G. Soumagne, A. Endo, H. Mizoguchi, A. Sumitani, K. Toyoda, Extreme Ultraviolet Lithography System Development Association (Japan)

- 65173C Small field exposure tool (SFET) light source [6517-124]

T. Abe, T. Suganuma, M. Moriya, T. Yabu, T. Asayama, H. Someya, Y. Ueno, G. Soumagne,

A. Sumitani, Extreme Ultraviolet Lithography System Development Association (Japan);

H. Mizoguchi, Gigaphoton Inc. (Japan)

65173D **Debris characteristics from a colloidal microjet target containing tin dioxide nano-particles** [6517-125]

T. Higashiguchi, S. Suetake, Y. Senba, Y. Sato, A. Hosotani, Y. Takahashi, S. Kubodera, Univ. of Miyazaki (Japan)

- A report on the modeling efforts in the development of a distributed EUV source for next-generation lithography tools [6517-126]

J. B. Spencer, Univ. of Illinois at Urbana-Champaign (USA); D. A. Alman, B. E. Jurczyk, Starfire Industries LLC (USA); D. N. Ruzic, Univ. of Illinois at Urbana-Champaign (USA)

- 65173G Experimental results for an addressable xenon microdischarge EUV source array for HVM lithography [6517-128]

B. Jurczyk, R. Stubbers, D. A. Alman, J. L. Rovey, M. D. Coventry, Starfire Industries LLC (USA)

- 65173I High-repetition-rate LPP-source facility for EUVL [6517-130]

T. Schmid, S. A. George, J. Cunado, S. Teerawattanasook, R. Bernath, C. Brown,

K. Takenoshita, C.-S. Koay, M. Richardson, College of Optics & Photonics/Univ. of Central Florida (USA)

- Laser-produced plasma source system development [6517-131]

I. V. Fomenkov, D. C. Brandt, A. N. Bykanov, A. I. Ershov, W. N. Partlo, D. W. Myers,

N. R. Böwering, G. O. Vaschenko, O. V. Khodykin, J. R. Hoffman, E. Vargas L., R. D. Simmons,

J. A. Chavez, C. P. Chrobak, Cymer, Inc. (USA)

- 65173K Gibbsian segregating (GS) alloys: a potential solution to minimize collector degradation [6517-132]

H. Qiu, S. N. Srivastava, J. C. Anderson, D. N. Ruzic, Univ. of Illinois at Urbana-Champaign (USA)

- 65173L **Debris mitigation techniques for a Sn- and Xe-fueled EUV-light source** [6517-133] K. C. Thompson, S. N. Srivastava, E. L. Antonsen, D. N. Ruzic, Univ. of Illinois at Urbana-Champaign (USA)

- 65173M Comparison of optical performances of alternative grazing incidence collector designs for EUV lithography [6517-134]

F. E. Zocchi, E. Benedetti, Media Lario Technologies (Italy)

- 65173N Simulation of EUV spectral emission from laser-produced tin-doped water plasmas [6517-135]

P. R. Woodruff, J. J. MacFarlane, I. E. Golovkin, P. Wang, Prism Computational Sciences, Inc. (USA)

- 651730 Characterization of the tin-doped droplet laser plasma EUVL sources for HVM [6517-136]

K. Takenoshita, S. A. George, T. Schmid, C.-S. Koay, J. Cunado, R. Bernath, C. Brown,

College of Optics & Photonics/Univ. of Central Florida (USA); M. M. Al-Rabban, Qatar Univ.

(Qatar); W. T. Silfvast, M. C. Richardson, College of Optics & Photonics/Univ. of Central

Florida (USA)

- 65173Q A mass-limited Sn target irradiated by dual laser pulses for an EUVL source [6517-138] Y. Tao, M. S. Tillack, K. L. Sequoia, F. Najimabadi, Univ. of California, San Diego (USA)

65173R Development of Sn-fueled high-power DPP EUV source for enabling HVM [6517-139]

Y. Teramoto, Z. Narihiro, D. Yamatani, T. Yokoyama, K. Bessho, Y. Joshima, T. Shirai, S. Mouri, T. Inoue, H. Mizokoshi, Extreme Ultraviolet Lithography System Development Association (Japan); G. Niimi, T. Hosokai, Ushio Inc. (Japan); H. Yabuta, K. C. Paul, T. Takemura, T. Yokota, K. Kabuki, K. Miyauchi, K. Hotta, H. Sato, Extreme Ultraviolet Lithography System Development Association (Japan)

Author Index

## Symposium Committees

Symposium Chair

Roxann L. Engelstad, University of Wisconsin/Madison (USA)

Symposium Cochair

Christopher J. Progler, Photronics, Inc. (USA)

#### Technical Organizing Committees

**Executive Committee**

John A. Allgair, SEMATECH, Inc. (USA) and Freescale Semiconductors (USA)

Chas N. Archie, IBM Corporation (USA)

Roxann L. Engelstad, University of Wisconsin/Madison (USA) Donis G. Flagello, ASML US, Inc. (USA) Clifford L. Henderson, Georgia Institute of Technology (USA) Michael J. Lercel, SEMATECH (USA) and IBM Corporation (USA) Harry J. Levinson, Advanced Micro Devices, Inc. (USA) Qinghuang Lin, IBM Thomas J. Watson Research Center (USA) Christopher J. Progler, Photronics, Inc. (USA)

Franklin M. Schellenberg, Mentor Graphics Corporation (USA) Vivek K. Singh, Intel Corporation (USA)

Alfred K. K. Wong, Magna Design Automation, Inc. (USA)

Advisory Committee

Robert D. Allen, IBM Almaden Research Center (USA)

William H. Arnold, ASML Netherlands B.V. (Netherlands)

Timothy A. Brunner, IBM Thomas J. Watson Research Center (USA)

Ralph R. Dammel, AZ Electronic Materials USA Corporation (USA)

Roderick R. Kunz, MIT Lincoln Laboratory (USA)

Harry J. Levinson, Advanced Micro Devices, Inc. (USA)

Burn Lin, Taiwan Semiconductor Manufacturing Company, Ltd. (Taiwan)

Chris A. Mack, LithoGuru.com

Victor Pol, Freescale Semiconductor, Inc. (USA)

Michael T. Postek, National Institute of Standards and Technology (USA)

Luc Van den Hove, IMEC (Belgium)

C. Grant Willson, The University of Texas at Austin (USA)

Anthony Yen, Taiwan Semiconductor Manufacturing Company, Ltd. (Taiwan) and Cymer, Inc. (USA)

## **Conference Committee**

Conference Chair

Michael J. Lercel, SEMATECH, Inc. (USA) and IBM Corp. (USA)

Conference Cochair

Franklin M. Schellenberg, Mentor Graphics Corp. (USA)

#### Program Committee

David T. Attwood, Jr., Lawrence Berkeley National Laboratory and University of California/Berkeley (USA) Vivek Bakshi, SEMATECH, Inc. (USA) Michael Goldstein, Intel Corp. (USA) Timothy R. Groves, Vistec Lithography Ltd. (United Kingdom) Woo-Sung Han, Samsung Electronics Co., Ltd. (South Korea) Hiroichi Kawahira, Sony Corp. (Japan) Bruno M. La Fontaine, Advanced Micro Devices, Inc. (USA) J. Alexander Liddle, Lawrence Berkeley National Laboratory (USA) Hans Loeschner, IMS Nanofabrication GmbH (Austria) **R. Scott Mackay**, Consultant (USA) Pawitter J. Mangat, Motorola, Inc. (USA) Christie R. K. Marrian, Spansion LLC (USA) Anthony E. Novembre, Lucent Technologies (USA) Laurent Pain, CEA-LETI (France) Kazuaki Suzuki, Nikon Corp. (Japan) William M. Tong, Hewlett-Packard Co. (USA)

Session Chairs

- Keynote Session

Franklin M. Schellenberg, Mentor Graphics Corp. (USA)

- 2 EUV Systems

Bruno M. La Fontaine, Advanced Micro Devices, Inc. (USA)

- Advanced Mask I

Emily E. Gallagher, IBM Microelectronics Division (USA)

Timothy R. Groves, Vistec Lithography Ltd. (United Kingdom)

- 4 EUV Optics **Patrick P. Naulleau**, Lawrence Berkeley National Laboratory (USA)

- 5 NIL I

William M. Tong, Hewlett-Packard Co. (USA)

J. Alexander Liddle, Lawrence Berkeley National Laboratory (USA)

- 6 EUV Source I Vivek Bakshi, SEMATECH, Inc. (USA)

- 7 EUV Imaging I **Kazuaki Suzuki**, Nikon Corp. (Japan)

- 8 Maskless Laurent Pain, CEA-LETI (France)

- 9 NIL II

**R. Scott Mackay**, Consultant (USA)

- 10 Joint Session with Conference 6519: EUV Resist Michael J. Lercel, SEMATECH, Inc. (USA) and IBM Corp. (USA) Anthony E. Novembre, Lucent Technologies (USA)

- 11 Advanced Mask II James W. Blatchford, Texas Instruments Inc. (USA)

- 12 Novel Lithography Hans Loeschner, IMS Nanofabrication GmbH (Austria)

- 13 EUV Imaging II **Michael Goldstein**, Intel Corp. (USA)

- 14 EUV Source II Akira Endo, Extreme Ultraviolet Lithography System Development Association (Japan)

## Lithography Beyond 32nm – A Role for Imprint?

#### Mark Melliar-Smith Molecular Imprints, 1807C West Braker Lane, Austin, Texas 78758 mark@molecularimprints.com

#### Abstract

Imprint lithography has been used since the application of the Chinese wax seal to authenticate official documents. In the past century the resolution of the technology has been driven through commercial applications such as vinyl records, CDs and more recently by high definition DVDs. In the past decade, high resolution imprinting has extended the resolution down to sub 10nm features and this fact, coupled with the low cost of the tool, make it attractive as an alternative to other lithographic technologies.

More recently the evolution of imprint lithography from thermal imprinting to UV cured materials, has allowed the technology to operate at room temperature (allowing tight overlay) and low material viscosities (important for high throughput), opening up the potential for CMOS applications. This paper will discuss recent progress in align/overlay, throughput, defect density, materials and the availability of sub 20nm templates, along with tool developments, that make the technology a viable option for advanced CMOS beyond 32nm HP design nodes.

In addition, imprint lithography is being developed for other large electronic markets such as bit patterned media (BPM) for disk drives, and photonic crystals to increase the brightness and efficiency of LEDs used for solid sate lighting, both of which applications are likely to go into production ahead of sub 32nm CMOS. Since overlay requirements are significantly less, whole wafer (as opposed to step and repeat) imprinting is used for these applications, and the presentation will discuss the synergies with CMOS imprint technology.

Key words: Imprints lithography, photolithography, bit patterned media, photonic crystals,

#### **1. Introduction**

Despite the remarkable progress made in the past decade in extending optical lithography to deep subwavelength imaging, the limit for the technology seems to be fast approaching. At 22nm half pitch design rules, neither very high NA tools (NA 1.6), nor techniques such as double patterning, are likely to be sufficient. The extension of photon based systems to EUV remains very challenging, and this has opened up the opportunity for imprint lithography as a very viable NGL alternative.

Small feature imprint lithography has existed for several years.<sup>(1-7)</sup> The original technique involved the use of a patterned template which is impressed onto a thermo plastic material and, with the combination of heat and pressure, the pattern in the template was transferred to the substrate.<sup>(2)</sup> Compact disks were one of the early applications for the technology. Recently the technique has been significantly improved with the development of Step and Flash Imprint Lithography (S-FIL<sup>TM</sup>).<sup>(1)</sup> This technique was invented by Professors Grant Willson and SV Sreenivasan at the University of Texas, and involves deposition of a low viscosity monomer on the substrate, lowering a template into the fluid which then flows into the patterns of the template. Following this fill step, the monomer is exposed to UV light to cross-link it and convert it into a solid, and the template is removed leaving the solid pattern on the substrate.<sup>(1,3)</sup> The advantages of this development (low pressure imprinting, low viscosity template filling and room temperature operation) make it uniquely capable for CMOS applications. Although this paper, and this conference, are largely focused on CMOS, it is worth noting that imprint technology can also be used in a wide variety of other advanced applications, many of which are only commercially viable given the availability of low cost (sub \$2M) tools capable of delivering sub 50nm features. These applications include the use of photonic bandgap crystals to

enhance LED efficiency and brightness, patterned media for disk drives, polarizers for projection optical engines and a wide variety of other electronic and photonic devices. For most of these applications the capital cost of 193nm immersion lithography is commercially untenable, even assuming that the required resolution limits could be reached.

The purpose of this paper is to describe the recent advances in imprint lithography with particular reference to its application for silicon integrated circuits.

#### 2. Imprint Technology for CMOS Applications

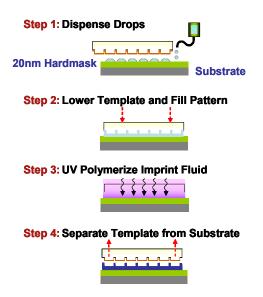

The S-FIL process is shown schematically in Figure 1. The process starts with a template made from a standard 6025 photomask blank, with the pattern etched into the glass using the same technology that is used for phase shift masks. An array of pico-liter sized drops of a low viscosity monomer, are spread across the field being imprinted and the template lowered onto the drops. When the surface tension of the liquid has been broken, capillary action draws the fluid into the template features. Once filling is complete, ultraviolet light, passing through the glass template, is used to cross link the monomer and convert it to a solid. The template can then be withdrawn and the process repeated on the next field.

The use of a low viscosity liquid has several advantages over spin-on films. Firstly, the lower viscosity of the liquid means that material movement and filling of the template are faster, particularly since the drop pattern density can be matched to the pattern density on the template. Secondly the process is intrinsically lower pressure – in fact controlled by capillary action, which also assures that the fluid does not spread outside of the template field. Finally, the use of the "drop on demand" technique prevents the requirement that spin coated wafers be passed into the tool – avoiding the problems of materials evaporation, particle collection on "wet" wafers and the need for a linked track. Since the pattern is "fixed" by UV light, the whole process can be completed at a controlled temperature allowing tight overlay between levels.

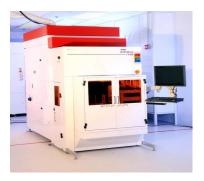

Molecular Imprints has commercialized the S-FIL technology, offering a CMOS compatible imprint tool – the Imprio- $250^{\text{M}}$  - which has been designed to take advantage of this type of imprint lithography, and offers the capability of mix and match with 193nm optical lithography with a 26mmx33mm field size, alignment/overlay and magnification control, automated imprint and FOUP to FOUP wafer handling. A photograph of the Imprio-250 is shown in Figure 2.

#### 3. The Advantages and Challenges for Imprint Lithography

Imprint lithography has a number of distinct advantages over photolithography when used for CMOS applications. These include:

(i) Lithographic capability

The imprint process appears to perfectly replicate the template. In consequence the template controls the resolution, line edge roughness and CD control of the imprinted pattern. Since the template has to be only written once, great care can be taken to assure its fidelity. Resolution limits appear to be less than 5nm. An example of research work from the University of Illinois <sup>(7)</sup> is shown in Figure 3, where a carbon nano-tube based template was replicated – if not perfectly. Since the monomer is of low molecular weight and is physically constrained by the template during solidification, there are none of the resolution/LER issues of molecular size, acid diffusion or areal image that are present in optical lithography. Other data/examples of lithographic quality are shown in Figures 10,12 & 13 and are discussed later in the text.

#### (ii) No OPC/RET/MEEF or design rule restrictions

Since the template is faithfully replicated by the imprint process – topics such as OPC and MEEF have no meaning in imprint lithography. While manufacturing a 1x template does present some additional challenges – it provides the device designer with complete freedom to design circuits without any lithography based design rules, freeing the designer from optical modeling artifacts. It is truly a "what you see is what you get" technology.

(iii) Lower capital cost

Since imprint tools lack the very complex lens and mirror systems inherent in photon based technologies, nor the need for a linked track, nor the requirement for vacuum and complex sources in EUV, the cost of the tools are significantly less than their competition. In addition, since they are largely mechanical tools, the build times are markedly less.

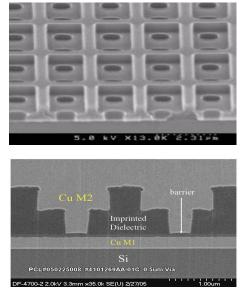

(iv) 3D printing

Since multi-level or curved features can be built into the templates, the technology has the capability for three-dimensional printing. This has the potential to extend the technology well beyond simple resist and etch capability and into the realm of single step imprinting of dual damascene structures (multilevel features) or direct imprinting of micro-lenses for CMOS imagining devices (curved features). These applications will be discussed later in the paper.

However, as might be expected, these advantages also come with a set of companion challenges. Confronting the technical challenges listed below is the topic of the main portion of this text, but they are listed below in summary form and to provide balance to the advantages.

- (i) 1x templates higher resolution, image placement and defect requirements as compared to 4x photomasks

- (ii) Defect concerns near contact printing

- (iii) Throughput in contrast to photolithography that simply requires exposure for each field, imprint requires not only exposure, but also material dispense, template fill, and field by field alignment.

- (iv) Overlay issues of mechanical magnification control

#### 4. Technical Progress in Imprint Lithography for CMOS Applications

#### 4.1 Templates

Imprint lithography uses templates made with commercial photomask materials and processes. This is a significant advantage relative to previous NGL technologies (X-Ray Proximity and Electron Beam Projection) that struggled with membrane based masks, or even EUV that requires new substrates and reflecting metal films. However, the 1X requirement does test resolution related issues – although not as near to the 4X that might come to mind. The advent of OPC features, which will soon be no more than 1.3x the minimum feature size on the wafer <sup>(8)</sup> are accelerating the resolution of mask ebeam writers. In addition for imprint templates, since the chrome is only being used as an etch mask (no optical opacity requirements), it is possible to use thinner chrome and ebeam resist than is typical to push resolution down to the required 1x. Image placement is also an issue for a 1x technology, but again, the approaching application of double patterning for 193nm immersion is pressing the existing photomask industry to meet very tight image placement specifications, even for nominally 4x photomasks.

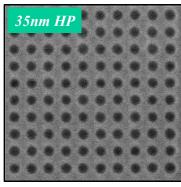

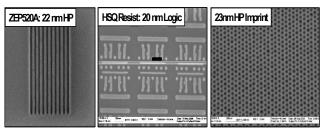

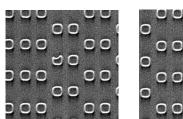

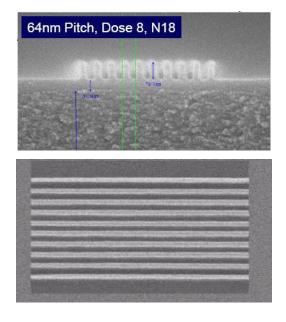

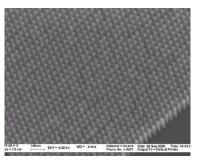

Using commercially available VSB mask writers, imprint templates are already being written down to 35nm dimensions, with very high quality, as shown in Figure 4a<sup>(9)</sup>. For higher resolution applications, imprint templates can be written with variants of ebeam direct write tools,<sup>(10)</sup> usually Gaussian Beam systems. These tools have unparalleled resolution, and can easily produce templates with dimensions of less than 20nm as shown in Figure 4b<sup>(11)</sup> providing an imprint resolution capability well beyond that possible with existing optical technologies.

However resolution is not the only issue for ebeam pattern generators, although it is the most compelling one for device/process development engineers pushing down below 30nm. Photomask write times have been rising rapidly in the past few years – victims of the huge data files required for advanced OPC. Templates have certain advantages in this area. Firstly there are no OPC features required, significantly reducing the number of shots required, and secondly, the area to be written is also a lot smaller. In addition, it is possible to "replicate" template patterns. In this process a single die template is made using an ebeam pattern generator, and then an imprint tool, such as the Imprio-250, is used to replicate this die to create a full field template containing multiple die. For a high volume runner, with four die per field and requiring five mask sets, the effective ebeam write acceleration would be a factor of 20 (four die X five mask sets). This technique has been used in the past for whole wafer, non-CMOS, imprint applications, and an example of the efficacy of the replication process is shown in Figure 5. The potential for lowering write times for imprint templates is important since it opens up the potential to use less sensitive ebeam resists to make the templates. This in turn allows templates with superior line edge roughness and higher resolution.

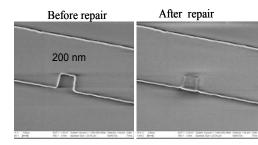

Template inspection and repair is also an issue since printable features are four times smaller than those for photomasks. To date the most sensitive template inspection techniques have used 1x wafer inspection tools. The KLA ES-32 tool has proved to be effective <sup>(12)</sup> in detecting sub 50nm defects using a die to die approach as shown in Figure 6a. For die to data base results, NGR <sup>(13)</sup> has been able to detect 20nm defects using its 2100 tool, as shown in Figure 6b. Repair of template defects can either be completed by mechanical removal of excess material <sup>(14)</sup> using a Rave 650NM tool, or by replacing missing material using a Nowatech MeRiTMG ebeam <sup>(15)</sup> enhanced deposition system. Examples of repair are shown in Figure 7. In the case of imprinting, the repairs are required to fill or remove material to a particular thickness, in contrast to a particular optical opacity. Small variations away from the nominal required dimensions are acceptable since this would simply mean that the imprinted resist thickness was slightly different from nominal.

#### 4.2 Alignment and Overlay

All imprint tools for CMOS applications must be designed to mix and match with existing 193nm optical lithography tools. This requires a step and repeat tool with a 26mmx33mm field size, alignment marks that fit into 75µm streets, alignment systems with sufficient contrast and show overlay results on top of 193nm printed under-layers.

The Imprio-250 uses a field by field alignment system, originally conceived for use in X-ray proximity printing, an earlier NGL technology.<sup>(16)</sup> This does not add to the imprint time since the alignment occurs during the time that the fluid is filling the template features. The "in liquid" align has the advantage that the imprint fluid acts both as a vibration damper and also a lubricant to facilitate the small motions required between the template and the substrate during alignment, reducing stiction effects.

Since the template and substrate are in close proximity ( $<10\mu$ m) during the alignment process, it is practical to capture the relative positioning error between two matching alignment marks using a Moiré image based technique<sup>(16, 17)</sup>. The advantage of using a 1<sup>st</sup> order Moiré image based technique is that it can provide high resolution alignment data using a low NA imaging unit (<0.05) without blocking the UV beam path. The alignment system utilizes multiple imaging units that can capture not only x, y, theta but also magnification errors. Utilizing the gap insensitiveness of the 1<sup>st</sup> order Moiré,<sup>(16, 18)</sup> alignment data can be captured throughout the template fill step and corresponding correction motions are accomplished in a

parallel manner. This system has demonstrated better than 1nm sensitivity of the alignment and positioning system. <sup>(16, 18)</sup>

Magnification correction is achieved by mechanically compressing the template. Positive magnification can be achieved by writing the template 5ppm oversize and releasing the compression. In this way the required +/- 5ppm can be obtained. Since the distortion is this small, well within the elastic regime of the material, it is perfectly reversible. A multi-point forcing mechanism was developed<sup>(19)</sup> that can induce optimized vectors of correction forces along the periphery of the template. Such an optimized forcing vector for the mag/distortion correction is computed using multiple relative position data between the template and the wafer that are captured using the alignment system described above. When n-points of forcing per template side are utilized, a vector with a 4n-3 controllability, where 3 stands for three constraints, is available. Therefore, a typical alignment for x, y, theta, mag x, mag y and orthogonality can be compensated.

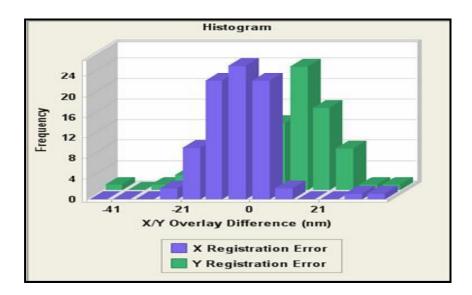

The efficacy of the alignment and magnification control systems were tested using a KLA overlay tool and AIM/Archer alignment marks. A sample set of results <sup>(20)</sup> are shown in Figure 8 with approximately 20nm 3 sigma overlay measured for 32 fields and 81 points per field. The major sources of the error are thought to be from thermal distortions, placement errors on the template and image field distortions from the 193nm scanner. Further improvements are expected to reduce the overlay errors down to 5nm.

#### 4.3 Throughput

While slower throughputs may be acceptable for early unit process development and device prototyping, it is clear that production needs of 20wph are required almost regardless of cost of ownership. This represents a challenge for imprint, since it is a multi-step process (fill, overlay, cure etc). The required budget to imprint a field at 20 wph is shown in Table 1.

| Table 1 – Field by Field Time Budget for 20wph |                          |  |  |

|------------------------------------------------|--------------------------|--|--|

| (100 fields/300                                | (100 fields/300mm wafer) |  |  |

| Stage move, fluid dispense time                | 0.15 seconds             |  |  |

| Alignment, template fill time                  | 1.00 seconds             |  |  |

| UV cure time                                   | 0.15 seconds             |  |  |

| Separation time                                | 0.10 seconds             |  |  |

| TOTAL                                          | 1.40 seconds             |  |  |

The most significant budget item, and the one specific to imprint, is the time required to fill the template. The two key parameters for fast fill are firstly, drop size and placement and secondly, the template contact angle to minimize any trapped air bubbles. In this latter respect, care must be taken to lower the template in a controlled and inclined angle such that the drops coalesce in a wave front that allows the gas between the drops to be swept out rather than trapped between the drops. The size and placement of the drops are carefully controlled to facilitate this. To do this, the drops, with a size of a few pico-liters, are dispensed using a linear array of several hundred inkjet nozzles that sweeps across the 26x33mm field. The density and pattern of the drops is optimized to the template pattern to minimize the amount of material movement required to fill the template features. Under optimal conditions fill times as low as 3 seconds have been achieved in the laboratory and further improvements are expected. The viscosity of the imprint fluid is also an issue relative to fill times. Acrylate based materials (see Section 5.1 below) have viscosities in the 5-10cps range, and other materials such as vinyl ethers are closer to 1 cps.

Future tool designs could use two other advantages inherent to imprint to improve the throughput. The ability to imprint larger field sizes could allow future systems to print four 26mmx33mm fields at once. This would place significant additional requirements on the template fabrication and overlay, but quadruple the throughput. In addition, since the cost of the imprint heads is minimal relative to optical lens stacks, multiple heads could be placed on a single stage platform, further increasing throughput, although multiple templates would be needed.

#### 4.4 Defects

There is concern about the defect levels inherent in imprint lithography since it is a near contact technology. However, it is an error to assume that the problem is similar to that of contact printing for the following reasons:

- (i) The template never actually touches the substrate. There is always a thin residual film of imprint material between the two surfaces.

- (ii) The imprint fluid drops, which have micron height, tend to cushion any impact between the template and particles

- (iii) The template is made from fused silica a hard and robust material.

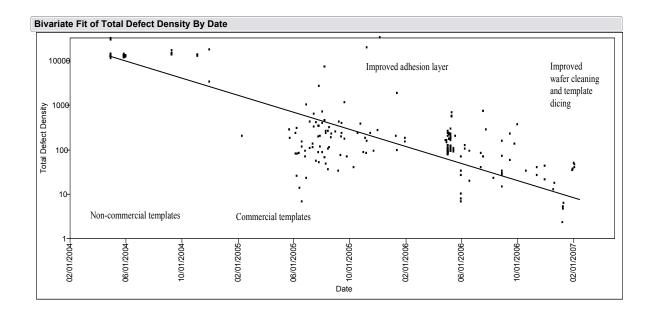

Significant progress has been made in reducing the defectivity of CMOS imprints. This progress is shown in Figure 9.<sup>(21)</sup> While still a considerable distance from what is ultimately needed for CMOS production, the progress has been sufficient for early device development activities. A Pareto analysis shows the defects to have three major sources: template defects, imprint specific defects and particles.

Template defects, as supplied by the commercial photomask vendors are, as might be expected, typically less than 1cm-2 as measured on a KLA 576 inspection tool. The template defect level is increased somewhat by the post photomask processing specifically required for templates (dice and polish, mesa preparation) but this does not represent an insuperable problem. The major challenge is to extend the life of the templates prior to their need to be removed from the imprint tool and re-cleaned. The templates do not "wear-out" since the fused silica is not eroded in anyway by contact with the imprint fluid. However, they can, over time, pick-up defects from partially cured monomer, or other contaminants, after several thousand imprints and need to be cleaned. Since the monomer is organic, the cleaning process is a standard oxidative clean, and early results for in-situ gas phase cleaning show some promise.

Imprint specific defects (micro-bubbles, imprint feature pull-outs etc) have been reduced to ~1cm-2. One important piece of data further suggests that these defects are not very dependent on defect size. A sample of imprinted patterns was tested on a KLA 2132 optical inspection tool with a 200nm pixel size and then retested on a KLA ES32 electron beam tool with a 25nm pixel size. The comparison of the results is shown in Table 2.

Table 2 – 200nm and 25nm Pixel Inspection Results

|                          | KLA 2132<br>(200nm) | KLA ES32<br>(25nm) |

|--------------------------|---------------------|--------------------|

| Template defects         | 4.8cm-2             | 6.0cm-2            |

| Particles                | 2.4cm-2             | 19.7cm-2           |

| Imprint specific defects | 0.0cm-2             | 0.0cm-2            |

Although this was an experiment with relatively low inspected area, the lack of defect size dependence for both the template defects and the imprint specific defects is very important since it suggests that the density of these defects is not strongly correlated with size. This is not altogether surprising when considered more deeply. For example micro-bubbles are know to be less stable the smaller they become, and imprint feature pull outs are more dependent on aspect ratio than feature size. The increase in particles as the resolution of the defect detection improved was to be expected. Further work in a cleaner environment, will reduce these numbers.

#### 5. Materials and Processes

For imprint lithography to be successful in CMOS, a complete solution must be available including materials and processes to complement the tool and templates.

#### 5.1 Materials

Successful imprint materials must be formulated with consideration for many requirements and the resulting formulations tend to be very sophisticated <sup>(22)</sup> to meet the severe yield demands for CMOS. The majority of the work described below is built around an acryate backbone, but vinyl ethers <sup>(23)</sup> have also been used.

One of the most basic challenges for imprint lithography is how to assure that the material sticks to the substrate and not to the template, even after many thousands of imprints. To reduce the surface energy of the template, a high surface concentration of fluorine is required, but this then restricts the wettability and filling speed, requiring a delicate balance. In addition, any coating on the template is liable to wear and tear, and an in-situ replenishment/repair process is required to keep the defectivity levels down. On the wafer surface, an adhesion promotion film can be used, but needs to be very thin (<2nm) and must be formulated to assure adhesion to multiple surface materials and also with a mind to wettability.

The cross linked material has to be drawn out of the template features during separation. This mandates a material with adequate mechanical strength, toughness and Young's Modulus to maximize the aspect ratio that can be used and yet completely prevent the possibility of a feature being left in the template. Adding polar components helps with these properties but excessive amounts increases the surface tension and reduces the fill speed. The etch resistance must be equivalent to the photoresists. The material must be formulated to be sensitive to UV radiation to assure fast curing, which means attention must be paid to the photoiniators, the wavelength of the exposing light and the prevention of oxygen inhibition.

Viscosity must be controlled. Low viscosities (<5cps) assist faster feature filling,<sup>(24)</sup> but higher viscosities (10-20cps) tend to be more favorable for ink-jet dispense into pico-liter drops. Lower viscosity materials tend to have high vapor pressures and evaporation rates which need to be minimized or compensated for.

Finally the purity of the material must meet the stringent CMOS requirements of <10ppb (metal ions), not just as formulated, but after passage through the inkjet head assembly.

#### 5.2 Process

For imprint to be successful for CMOS, the tools must not only mix and match with 193nm optical tools, but the imprint materials and processes have to be compatible with the upstream and downstream CMOS processing as well. Most CMOS customers want to place the imprint process into their integrated process without any changes – essentially a drop in replacement for optical lithography.

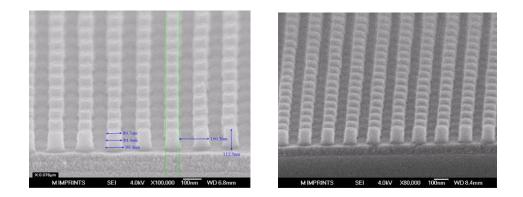

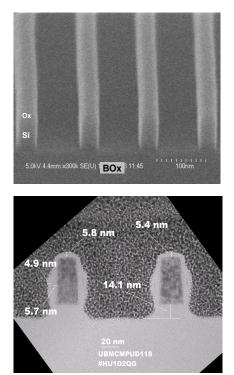

This has been achieved with the use of the SFIL-O process shown in Figure 1. In this process the organic imprint material has been formulated to be an effective etch mask for silicon based films, and the imprint process tuned to the point where the residual organic layer between the imprinted features is both very thin (~15nm) and very uniform (<5nm  $3\sigma$ ). Since the imprinted features have a typical height of over 50nm (2.5:1 aspect ratio for 22nm HP features), the residual layer can be removed with a quick "de-scum" oxygen etch, prior to etching the hard mask with a fluorine based etch. Typical results for hard mask etching are shown in Figure 10.<sup>(25)</sup> Excellent resolution, line edge roughness and sidewall angle are routinely achieved. Typical etch ratios between the imprinted material and the underlying hard mask are designed to mimic 193nm photoresists, so that the etching processes can be very similar.

An alternative process called SFIL-R<sup>(26)</sup> has been developed to provide a positive image of the template on the substrate (as opposed to the negative working SFIL-O process). In this case, following imprinting, a silicon containing film is spun on top of the imprinted features, effectively planarizing the surface. A blanket etch back of the silicon film is made until the imprinted organic features are exposed. At this point the etch chemistry is changed to an oxidative etch which then removes the underlying imprinted features, but leaves the silicon containing material between them intact to act as an etch mask. The SFIL-R process has the advantage of being less sensitive to surface topography on the substrate.