## International Conference on Space Optics—ICSO 2020

Virtual Conference

30 March-2 April 2021

Edited by Bruno Cugny, Zoran Sodnik, and Nikos Karafolas

# The ESA project PIOTS: setting up a complete pilot line for the packaging of photonic integrated circuits for space applications

International Conference on Space Optics — ICSO 2020, edited by Bruno Cugny, Zoran Sodnik, Nikos Karafolas, Proc. of SPIE Vol. 11852, 118525G · © 2021 ESA and CNES CCC code: 0277-786X/21/\$21 · doi: 10.1117/12.2599959

### THE ESA PROJECT PIOTS: SETTING UP A COMPLETE PILOT LINE FOR THE PACKAGING OF PHOTONIC INTEGRATED CIRCUITS FOR SPACE APPLICATIONS

D. Rotta\*a, G. B. Preve<sup>a,b,c</sup>, A. Serrano Rodrigo<sup>a</sup>, M. Chiesa<sup>a</sup>, G. Cucinella<sup>d</sup>, A. Bogoni<sup>a,b,c</sup>

<sup>a</sup>Inphotec Foundation, via G. Moruzzi, 1 – 56124 Pisa – Italy; <sup>b</sup>TeCIP Institute, Sant'Anna School of Advanced Studies, via G. Moruzzi, 1 – 56124 Pisa – Italy; <sup>c</sup>CNIT, via G. Moruzzi, 1 – 56124 Pisa – Italy; <sup>d</sup>IMT srl, Via Carlo Bartolomeo Piazza, 30 – 00161 Roma – Italy

#### ABSTRACT

Photonic Integrated Circuits (PICs) are expected to have a primary role for space applications in the years to come. The growing interest for the PICs for space applications lays in the fact the integrated photonics brings notable advantages as, among others:

1) Size, Weight and Power (SWaP) reduction

2) Removal/reduction of electromagnetic interferences

3) More flexibility (e.g. Network-on-chip)

4) Convergence with integrated electronics with potential costs reduction and improved performance (e.g. Beamforming)

5) Possibility to avoid optical to electronic to optical conversions (O-E-O) by maintaining some functions at photonic level in the optical domain, like for example in optical beamforming and photonics-based up- and down-conversion

However, photonic packaging is less mature than its microelectronic counterpart. In fact, considering the great advancements in designing and fabricating integrated photonic chips, photonic packaging still represents a limiting factor and requires dedicated effort especially in view of a full exploitation of integrated photonics for Space applications.

There is necessity to develop the proper packaging technologies compatible with the Space requirements as well the proper packaging line processes controls and documentations. PIOTS project aims to answer such demand by creating an end-to-end packaging pilot line that is strategically oriented to the demands of ESA and European space industry. This goal will be demonstrated through the realization of two test vehicles and the validation of manufacturing processes, equipment & techniques by means of an adequate Quality System implementation, including documentation and in-line controls as required to manufacture a product complying with requirements of the space sector.

The paper will update on the project status focusing on the two test vehicles:

TV1 - a hermetically packaged laser integrated with a SOI device

TV2- a hermetically packaged SOI device with 8 in/out pigtailed fibers

Keywords: Photonic packaging, integrated photonics, evaluation testing, capability approval, satellite telecommunication, new space economy

\*davide.rotta@inphotec.it

#### 1. INTRODUCTION

Photonics has rapidly penetrated the space market since the '60s when reliable low-weight and limited-size optical equipment became available. Up to now, most of the efforts have been focused on mono-satellite missions and on satellites for single missions (Earth and deep space observation, military surveillance, meteorological complementary observations and telecommunication).

Recent development of telecommunication systems paved the way to novel commercial space applications (new space) with different requirements and potential: life-limited, low cost to launch, easy access. In fact, photonics allows to integrate RF and optical communication functionalities that can be exploited both for Earth Observation data relay (especially the RF link) and telecommunication operations as inter-satellite communications or deep space communications [7][8].

Inter-satellite communications (hybrid optical/RF) are becoming more and more important especially for small satellite constellations. To this regard, integrated photonics systems sharing the optical and the RF hardware may have the potential to reduce Size, Weight and Power (SWaP) of the payload, besides exploiting a potentially cheaper and more scalable technology. Photonics can be used not only for optical transceivers, but also to provide frequency flexibility and high performance in software-defined RF transceivers. In both photonics-based radio detection and ranging (radar) and RF communication transceivers the electrical circuit is replaced by a fully optical one, avoiding Optical to Electronic to Optical (O-E-O) conversion and the consequent extra-losses and power consumption [9][10]. Moreover, it could be possible to integrate different mission functionalities on the same satellite (i.e., integrate two missions in one mission). In fact, a combined radar/lidar system will have enhanced performance and, at the same time, the capability to capture heterogeneous data in uniform detection conditions exploiting a single system. Also in this case, sharing of the same integrated system will allow for a reduced SWaP and Cost (SWaP-C) of the system.

All these new applications could take advantage from using constellations of small satellites with capability of providing flexible and heterogeneous data. Photonics offers a great potential for the development of such multi-mission small satellites, and missions based on small satellite constellations. Integrated photonics in particular is the natural evolution on such technology roadmap. However, its full exploitation is mainly hindered by the technological constraints of photonics packaging. Most of the value of microelectronics devices typically resides in the fabrication of the integrated photonics takes advantage of decades of technological advancement in CMOS fabrication, but from the packaging point of view it raises additional challenges including the realization of low-loss optical coupling with fiber optics, which requires sub-micron alignment accuracy. Moreover, even the most mature technology platform, namely Si photonics, offers a complete toolbox of consolidated building blocks, but still lacks of a laser source [11]. In fact, efficient laser integration remains one of the main technological challenges on the technological roadmap of Si photonics.

Packaging constraints get even more demanding in space photonics, where additional requirements arise from the integration of the photonic devices in complex payloads and from the stringent mission-related requirements. Guaranteeing operation and storage in extended temperature ranges (often larger than in terrestrial telecom standard), protection from moisture and radiation and tolerance against the dramatic vibration of launching sequence constitute the main criticalities in the design and evaluation of a space-qualified photonic device. At present, few research projects and companies have proposed ruggedized photonic components as lasers, modulators and photodetectors, or integrated optical transceiver systems for intra-satellite communication [1][2][3][4][5][6]. Most of the achieved results concern the development of single space-compliant devices, while lower efforts have been done for integrating space-grade entire systems/subsystems. This is mainly due to technical issues, not completely addressed and solved, concerning packaging of heterogeneous photonic components in hybrid technologies with consolidated fiber optics interface. Nowadays the heritage of integrated photonics packaging technologies for space applications is still quite young and fragmented in Europe (as well as worldwide) so a consolidated technology does not exist yet to answer properly to the challenges posed by this new line of potential products. The only way to exploit the mentioned advantages of photonic integration in space will consist in mastering a suitable packaging technology platform that is capable of meeting the requirements set by the Space Agencies.

PIOTS project, funded by the European Space Agency under GSTP program 4000125664/18/NL/GLC/fk, aims to create and demonstrate an end-to-end packaging line at INPHOTEC technology center that shall include packaging manufacturing processes, equipment and techniques required to manufacture products for the space sector. The technologies developed within INPHOTEC pilot line will be validated through dedicated evaluation testing and qualified

through a proper quality management system, enabling integrated optoelectronic and photonic packaging in line with the applicable ESCC and ECSS documents as required by ESA.

The article is organized as follows. The next Section presents the PIOTS project and its main objectives, including the upgrade of INPHOTEC packaging pilot line with novel equipment, technologies and quality management systems. Following, the two devices at the core of the project, namely the Test Vehicles TV1 and TV2, will be presented as the benchmark for the space-grade qualification of INPHOTEC pilot line, focusing on the problems of laser integration and multiple fiber optics I/O. Then, an overview of the testing activities will be presented, discussing the main critical points in relation with ESA requirements. Finally, preliminary results of PIOTS will be presented and discussed in view of the final qualification of INPHOTEC packaging pilot line for space applications.

#### 2. THE PIOTS PROJECT: GOAL AND METHODOLOGIES

The objective of PIOTS is the demonstration of a packaging manufacturing line for photonic space applications through the implementation of relative integration procedures, in-line controls and quality documentation as requested by space applications. In order to benchmark the expected capabilities of the packaging line, the project will design and assemble two Test Vehicles (TV) with the aim to demonstrate their conformity (in all applicable cases) with ESA requirements as reported in the document "ESCC Basic Specification No. 2566000 – Requirements for the process capability approval for manufacturing line of hermetic hybrid microcircuits".

From the technological point of view, the starting point is the existing terrestrial packaging line operative at INPHOTEC facilities for PIC devices, which relies on industrial-grade equipment for an approximate total value of 2.5M€. The main equipment is constituted by:

- an automatic ball-wedge wirebonding machine,

- a multipurpose die-bonder supporting epoxy-based as well as solder reflow processes,

- an automatic pigtailing bench for active alignment of two fiber arrays

- an automatic flip-chip bonder with sub-micron accuracy for wafer scale laser-assisted bonding processes

- a pull-shear tester

The hybrid co-packaging of lasers, photodiodes, SOAs and more III-V components in chip on SOI is part of INPHOTEC expertise. Their advanced packaging lab is able to package active and passive optical and RF components implemented on different technological platforms, microoptics and other hybrid devices for terrestrial applications. An important feature is the high degree of process automation that is possible with the available equipment, which allows early-stage prototyping as well as small-scale production thanks to an adequate process consistency and repeatability, resulting in improved reliability and quality of the final product. The existing INPHOTEC terrestrial packaging line has been completed with the acquisition of selected equipment, such as an hermetic parallel seam welding sealer and a local heating soldering system to fill in the gap regarding hermeticity, as requested by space photonics packaging.

During the project timeline, ESA manufacturing guidelines will be implemented for the design and realization of two test vehicles that are respectively:

- TV1 III-V hybrid integration. TV1 addresses the integration of a laser source through active alignment of free-space microoptics and of an InGaAs photodiode on an SOI photonic chip through solder reflow bonding. The device includes a thermo-electric cooler (TEC) for thermal stabilization and is packaged in a hermetic package with electrical feedthroughs.

- TV2 Multiple fiber optics I/O. TV2 demonstrates the capability of multiple optical input/output to an SOI PIC via a hermetic optical feedthrough. At present, photonic multiple IN/OUT fiber interfaces for terrestrial applications are inherently not hermetic.

The two test vehicles constitute the test-bench where the ESCC and ECSS basic requirements are applied for the choice of the declared parts and materials, the definition of their Manufacturing, Assembly, Integration and Testing (MAIT)

procedures and flow chart, the definition of inspection procedures with pass/fail criteria and more generally the implementation of a solid quality assurance system.

To summarize, PIOTS project targets a high level standard in:

- EQUIPMENT: upgrading the available terrestrial packaging technologies including hermetic sealing equipment and hermetic oriented processes as well to upgrade the testing and reliability tools,

- MANUFACTURING: designing and assembling the two test vehicles that will be packaged to demonstrate the new packaging line capability after dedicated process development,

- QUALITY: demonstrating and validating methods of manufacturing, developing inspection and validation methods to be documented and deployed in line with ECSS and ESCC requirements,

- TESTING: evaluating the test vehicle packaged devices with a proper test plan according to space packaging requirements in agreement with ESA.

#### 3. TV1 – HYBRID INTEGRATION OF III/V DEVICES

One of the main challenges in silicon photonics is the integration of active devices, in particular lasers. Several approaches have been proposed, both monolithic (i. e. the III-V semiconductor is grown on the silicon wafer and processed at wafer level) and hybrid (i.e. the active components are realized separately and bonded to the SiPh chip). In our test vehicle TV1 we propose a package level integration approach based on active alignment of micro-optics combined for laser integration and flip-chip soldering for photodiode attachment. The PIC has basic functionalities, so as to focus the efforts on developing the technology platform for a wide variety of devices and applications.

In our design, an edge emitting laser diode is coupled into the PIC by means of a two-lens system, where the first one collimates the beam and the second one focuses it onto the PIC edge coupler similarly to the typical scheme of commercial Transmitter Optical Sub-Assembly (TOSA) devices. One of the advantages of this scheme is the possibility to integrate an optical isolator as well, to avoid back reflections onto the laser. Moreover, the availability of custom-design microlenses is highly effective in allowing a flexible design of the PIC on one side and leaving free choice of the laser diode on the other side, making possible to choose consolidated Commercial Off The Shelf (COTS) parts.

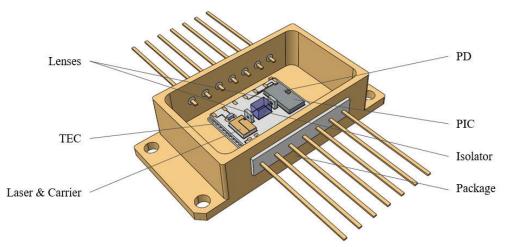

Figure 1 TV1 package layout. Package lid not shown.

Figure 1 shows the package layout of TV1 assembly. We use a common substrate for the laser diode, the PIC, the isolator and the lenses, to reduce possible coupling losses arising from different thermal expansion between parts; this common substrate coincides with the cold side of the thermoelectric cooler (TEC) used to maintain the laser temperature within the operating specs. The TEC cold side has a metal pattern for electrical routing between the package pinouts and the other active parts. The PIC is a simplified circuit realized within INPHOTEC Si-hybrid integration platform. A single waveguide is terminated by an edge coupler at the input side and by a grating coupler at the output side, where an InGaAs photodiode is flip-chip soldered to monitor the intensity of the light coupled into the chip. Gold-tin ( $Au_{80}Sn_{20}$ ) solder pads are lithographically defined and deposited by electron-beam evaporation on the PIC. Although the integration of photodiodes is often available as a monolithic building block at many SiPh foundries, in this case we opted for a hybrid approach to demonstrate hybrid integration in both vertical and edge coupling layouts.

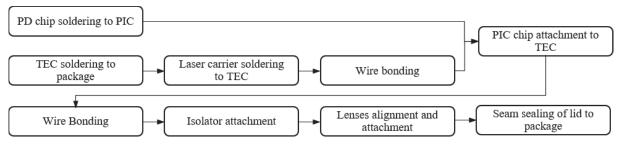

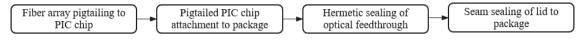

Figure 2 TV1 Manufacturing flow chart

Figure 2 shows the assembly process flow of TV1, which is explained in the following. The first step is flip-chip soldering of the photodiode on the PIC, as it requires the highest thermal budget (the eutectic melting temperature is 280°C). In parallel, the TEC is soldered to the package by oven reflow using a solder preform. Then, the laser diode, which is pre-assembled on a ceramic submount, is passively aligned and soldered to the TEC cold side. The PIC with the soldered PD is assembled on the TEC cold side by adhesive bonding, using a standard conductive epoxy (Epo-Tek H20E) to improve thermal contact. The electrical connections from the components (TEC, laser diode, thermistor, photodiode) to the package are realized by ball bonding using gold wire, using in some cases routing lines defined on the TEC cold side or, in the case of the PD, on the PIC. The isolator is then tacked to the common substrate and the two lenses are actively aligned and attached by a low stress UV+thermal adhesive. Finally, the package is hermetically sealed in nitrogen atmosphere by resistive seam welding so as to protect the sensitive active devices and the optical path from moisture and contaminants.

In order to reduce the outgassing of the resins, we make use of solder-based die bonding techniques where possible, limiting the use of adhesive bonding only where there is no alternative. In these cases, the adhesives were chosen in order to comply with the outgassing requirements ECSS-Q-ST-70-02C.

#### 4. TV2 – MULTI-CHANNEL FIBER OPTICS INPUT/OUTPUT

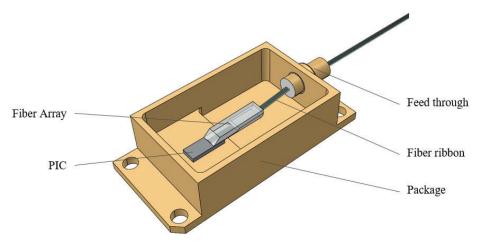

At the present the pigtailing of multiple-way fiber-arrays is a well-developed technology for terrestrial applications, however this cannot be easily exported to space application due to the stringent environmental requirements, leading to a hermetic package. As a consequence, providing a hermetic feedthrough is of paramount importance for integrated photonics applied to space systems. During the PIOTS project, the TV2 package layout has been designed to fulfill this requirement by providing an effective fiber optics interface while preserving the overall hermeticity of the packaged device. In details, Figure 3 represents the CAD model of TV2, which consists of a simplified SOI PIC attached within the cavity of a kovar hermetic package and pigtailed with an array of 8 single mode fibers. Our strategy relies on a special fiber array equipped with a cylindrical hermetic feedthrough, which fits the circular aperture on the sidewall of a kovar package. Hermeticity is then guaranteed by a solder joint between the package aperture and the Au-coated cylinder feedthrough.

Figure 3 Package layout of TV2. Package lid not shown.

Analogously to TV1, the TV2 PIC has basic functionality in order to focus on the reliable demonstration of the package technologies: an 8 grating coupler array represents the optical interface of a typical PIC, which in this case is reduced to the simplified layout of four passive waveguide loops. Although grating couplers bring the great advantages of easy fabrication and relatively large alignment tolerances, from the point of view of package layout the drawback is represented by the small coupling angle from the vertical axis (typically 8-11°) that leads to a high aspect ratio packaging layout featuring a long fiber array vertically attached to the PIC surface. This is hardly compatible with compact packaging solutions and small fiber feedthrough, making the hermetic sealing increasingly difficult. To mitigate the mentioned drawbacks, a low form factor fiber array based on Total Internal Reflection (TIR) has been selected to enable a quasi-planar optical coupling scheme.

Geometrical and physical properties of the solder joint at the fiber feedthrough are key to obtain a high-reliability hermetic sealing. Different factors shall be considered in the soldering technology selection: material compatibility of the package frame and feedthrough coating in terms of solder surface wettability; possible outgassing issues caused by use of fluxes; thermal budget of the different components and materials (including the fiber optics assembly); solder amount and package to fiber clearance are all important factors to guarantee the required mechanical stability and uniformity of the joint.

Another important aspect to be considered during the design of space grade components is the reduction of the use of outgassing materials, like the epoxies used for the pigtailing and die attachment. Low outgassing epoxies has been selected to carry out mentioned assembly processes.

Figure 4 TV2 Manufacturing flow chart

Regarding the assembly process flow, shown in Figure 4, the first step is pigtailing of the TIR fiber array to the PIC. Then, the pigtailed PIC is introduced through the package aperture and attached to the package base by means of a thermally conductive epoxy. The next step of the process is the hermetic sealing of the optical feedthrough by means of a solder joint. The package is finally sealed with a metal lid by means of parallel seam welding technology similarly to TV1.

#### 5. VALIDATION TESTING

Demonstration of Test vehicle conformity with ESA requirements is based on "ESCC Basic Specification No. 2566000-Requirements for the process capability approval for manufacturing line of hermetic hybrid microcircuits".

The test vehicles are encapsulated with the actual packaging technique.

The test vehicle are designed to evaluate:

- The main electrical parameters related to the added-on passive and discrete active components (and integrated circuits, if possible)

- The mechanical (and electrical, when applicable) performance of attachment medium (adhesive bonded or soldered joints)

- The mechanical and electrical performance of bonding wires or ribbons

- The behaviour of the encapsulation with respect to the environmental stresses (thermo-mechanical, humidity, contamination)

A reference device of each type of test structure is kept for comparison purposes. Whenever electrical measurements are performed on any test structure during evaluation testing the reference device of the same type will also be measured.

A supplementary test vehicle will be used for initial destructive physical analysis (DPA) including internal water-vapor content test.

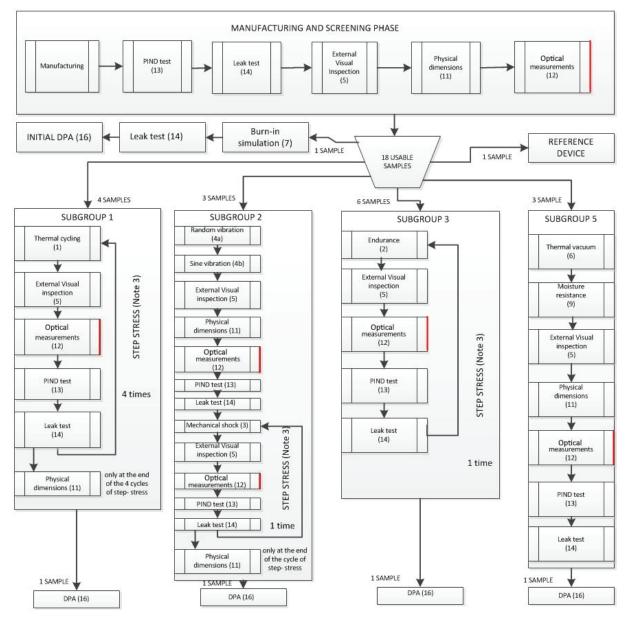

The Evaluation Plan to be applied for test vehicles is based on the following chart (Figure 5).

Figure 5 PIOTS Evaluation Test Plan

The test methods and conditions applicable to test vehicles are described in the table below.

| External Visual Inspection                                             | Physical dimensions                                                   |

|------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Test Method: MIL-STD-883 T.M. 2009                                     | Test Method: MIL-STD-883 T.M. 2016                                    |

| Requirements:                                                          | Requirements:                                                         |

| - Devices shall be examined at 10X magnification                       | - According to test vehicle Technical specification.                  |

| minimum.                                                               |                                                                       |

| PIND Test                                                              | <b>Optical / Physical Measurements</b>                                |

| Test Method: MIL-STD-883 T.M. 2020                                     | Test Method: Optical / Physical Performance                           |

| Requirements:                                                          | characteristics                                                       |

| - Condition A                                                          | Requirements:                                                         |

|                                                                        | - As per datasheet                                                    |

| Electrical / Optical/ Physical Measurements                            | Thermal cycling                                                       |

| Test Method: Electrical / Optical/ Physical Performance                | Test Method: MIL-STD-883 T.M. 1010 Condition B                        |

| characteristicsr                                                       | Requirements:                                                         |

| Requirements:                                                          | - 100 cycles per step up to 500 or failure                            |

| - As per datasheet.                                                    |                                                                       |

| Terminal Strength (on TV1, only)                                       | Endurance                                                             |

| Test Method: MIL-STD-883 T.M. 2004                                     | Test Method: MIL-STD-883 T.M. 1005                                    |

| Requirements:                                                          | Requirements:                                                         |

| - Rigid feed-throughs in packages:                                     | - Duration 1000h + 1000h. Ambient temperature will be                 |

| - Diameter $\leq 1$ mm; condition A, F (N) = 30 x S (mm <sup>2</sup> ) | defined to achieve $125^{\circ}C \le Tj \le 150^{\circ}C$ (or maximum |

| (F: strength, S : lead section)                                        | ratings). If the Tj of the most stressed part is lower than           |

| - Diameter > 1mm, condition C1, torque :1,5 N.cm                       | $125^{\circ}$ C, the time shall be increased according to MIL-        |

| - Diameter > Thini, condition C1, torque .1,5 N.em                     | STD-883 Method1005.                                                   |

| Leak Test                                                              | Solderability (on TV1, only)                                          |

| Test Method: MIL-STD-883 T.M. 1014                                     | Test Method: MIL-STD-883 T.M. 208                                     |

| Requirements:                                                          | Requirements:                                                         |

| - Fine leak: condition A Gross leak: condition C                       | - Three terminals per test item                                       |

| Burn-in Simulation                                                     | Moisture Resistance                                                   |

|                                                                        | Test Method: MIL-STD-883 T.M. 1004                                    |

| Requirements:<br>- Bake during 240 h at 125 °C, no voltage             | Requirements:                                                         |

| - Bake during 240 fr at 125°C, no voltage                              | 1                                                                     |

|                                                                        | - 10 V DC between all terminals connected together and                |

|                                                                        | package (+ on terminals)                                              |

| Sine Vibration                                                         | Random Vibration                                                      |

| Test Method: MIL-STD-883 T.M. 2007                                     | Test Method: MIL-STD-883 T.M. 2026                                    |

| Requirements:                                                          | Requirements:                                                         |

| - Condition B, 50 g                                                    | - Condition I K, Random Vibration 44.8 g RMS, 3 axis                  |

| DPA                                                                    | Mechanical Shock                                                      |

| DPA will be performed according to the following Steps                 | Test Method: MIL-STD-883 T.M. 2002                                    |

| (as per ESCC 2566000):                                                 | Requirements:                                                         |

| - External Visual inspection; - Radiography; - Residual                | - Step1 Condition B (1500g) for packages up to 1" x 2"                |

| gas analysis; - Delidding; - Internal visual inspection;               | and1000 g 0,5 ms for packages above.                                  |

| - SEM Inspection; - Bond pull test; - Die shear test                   | - Step 2: Condition C (3000g) for packages up to 1" x 2"              |

| - Micro- sectioning                                                    | and Condition B (1500g) for packages above.                           |

|                                                                        | - Shocks performed on Y1, Y2, X and Z axes                            |

|                                                                        |                                                                       |

#### 6. **DISCUSSION**

INPHOTEC has extensive experience in packaging techniques for terrestrial telecom applications, which are employed in TV1 and TV2 manufacturing process flow. However, dealing with space applications, some steps in the process flow turns out to be extremely delicate in terms of space-grade reliability and represent critical issues to be addressed at an earlier stage with dedicated evaluation models (EVM).

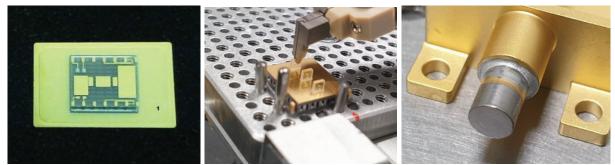

For example, the reflow soldering of the TEC was developed and validated separately because of the inherent risk of voids in the solder due to the large area of the component (about 100 mm<sup>2</sup>). Particular care was devoted to the cleanness of the parts to be joined, including the use of formic acid as a reducing agent. Similar considerations apply to the attachment of micro-optics in TV1 because of their high aspect ratio and to the hermeticity of the fiber feedthrough in TV2, so dedicated EVM have been defined in PIOTS development plan, as shown in Figure 6. In particular, for what concerns TEC soldering, preliminary results from X-ray inspection indicate the presence of voids in less than 30% of the joint area, whereas rejection criteria set a maximum of 50%.

Figure 6 Development and validation of critical manufacturing process steps through EVM. (Left) TEC soldering. (Center) Microlens attachment on a TEC substrate. (Right) Hermetic soldering of fiber feedthrough. The fiber array is substituted by a metal cylinder for evaluation testing of the joint hermeticity.

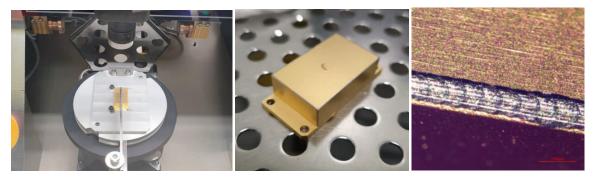

Besides, hermeticity is of paramount importance in space optical packaging, as mentioned above. For this reason, the installation of a state of the art parallel seam welding equipment at INPHOTEC advanced packaging laboratory constitutes a major milestone of PIOTS project. Furthermore, the first EVM has been dedicated to the development and validation of the seam welding technology. The first batch of EVM, featuring a simplified gold box with a flat lid similar to TV1 and TV2, is shown in Figure 7. Hermetic sealing was confirmed by standard leak testing according to MIL-STD-883, TM 1014. After gross and fine leak testing, all the samples passed the test with leakage lower than 1E-08 atm cc/s.

Figure 7 Process development of hermetic seam welding of PIOTS packages. (Left) Wide view of the parallel resistive welding equipment while processing an EVM package. (Center) EVM package after hermetic seam sealing process. (Right) Detail of the weld joint on a sealed EVM package.

Further process development and advanced testing are actually proceeding according to the EVM test plan, including microsections and thermal cycling on the different EVM devices in order to consolidate the technology background before the assembly of TV devices. The entire process development and evaluation testing is supported in parallel by the creation of a quality management system, featuring the typical project management documentation and manufacturing assembly inspection and testing (MAIT) procedures in line with ESCC and ECSS standards. This framework has been set in agreement with ESA after the fulfillment of a Preliminary Design Review in 2019 and will be periodically reviewed by ESA during the following reviews before the final approval at the end of project in 2022. The fulfillment of the PIOTS project goals will contribute to a new era of space technology in Europe by providing a unique space packaging provider specialized in integrated photonics and consequently enabling a new generation of space devices based on integrated optics.

#### ACKNOWLEDGEMENTS

The authors acknowledge European Space Agency (ESA) and Italian Space Agency (ASI) for technical and financial support with PIOTS project (GSTP program 4000125664/18/NL/GLC/fk).

#### REFERENCES

- [1] http://goochandhousego.com/news/beacon-photonics-for-telecom-satellites/

- [2] http://www.fp7-hippo.eu/

- [3] http://www.zephyrphotonics.com/wide-temperature-vcsels.html

- [4] http://www.ultracomm-inc.com/projects/

- [5] https://www.radiall.com/media/files/Section\_10\_Web3.pdf

- [6] http://reflexphotonics.com/aerospace-defence/

- [7] R. Lange and B. Smutny, "Homodyne BPSK-based optical inter-satellite communication links," Free-Space Laser Communication Technologies, 2007.

- [8] H. Hemmati, A. Biswas, and I. B. Djordjevic, "Deep-Space Optical Communications: Future Perspectives and Applications", Proceedings of the IEEE, vol. 99, no. 11, pp. 2020-2039, Nov. 2011.

- [9] P. Ghelfi, et al., "A fully photonics-based coherent radar system," Nature, vol.507, 2014.

- [10] P. Ghelfi et al., "Photonics in Radar Systems: RF Integration for State-of-the-Art Functionality," IEEE Microwave Magazine, vol. 16, no. 8, 2015.

- [11] P. Dong, et al. "Silicon photonic devices and integrated circuits," Nanophotonics, vol. 3, no. 4-5, 2014.